# **SUPER**<sup>®</sup>

# SUPER i2DMR-8G2 SUPER i2DMR-iG2

# **USER'S MANUAL**

**Revision 1.0**

The information in this User's Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates.

# Please Note: For the most up-to-date version of this manual, please see our web site at www.supermicro.com.

SUPERMICRO COMPUTER reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software, if any, and documentation may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any medium or machine without prior written consent.

IN NO EVENT WILL SUPERMICRO COMPUTER BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, THE VENDOR SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA.

Any disputes arising between manufacturer and customer shall be governed by the laws of Santa Clara County in the State of California, USA. The State of California, County of Santa Clara shall be the exclusive venue for the resolution of any such disputes. Supermicro's total liability for all claims will not exceed the price paid for the hardware product.

Unless you request and receive written permission from SUPER MICRO COMPUTER, you may not copy any part of this document.

Information in this document is subject to change without notice. Other products and companies referred to herein are trademarks or registered trademarks of their respective companies or mark holders.

Copyright © 2003 by SUPER MICRO COMPUTER INC. All rights reserved. Printed in the United States of America

# Preface

# **About This Manual**

This manual is written for system integrators, PC technicians and knowledgeable PC users. It provides information for the installation and use of the SUPER i2DMR-8G2/i2DMR-iG2 motherboard. The SUPER i2DMR-8G2/ i2DMR-iG2 supports single or dual Intel Itanium<sup>®</sup> 2 processors at a 400 MHz front side bus. Uniquely designed for demanding enterprise and technical applications, the Itanium 2 processor with 6 MB L3 Cache can provide performance increases of up to 30 to 50 percent or more over the original Intanium 2 processor. With its massive execution resources, 6.4GB/sec system bus bandwidth and 1.5GHz core speed, the latest Itanium 2 processor offers high-end reliability, flexibility, and scalability features for business critical computing and the most data-intensive applications. Please refer to the motherboard specifications pages on our web site (http://www.supermicro.com/Product\_page/product-m.htm) for updates on supported processors. This product is intended to be professionally installed.

# **Manual Organization**

**Chapter 1** begins with a checklist of what should be included in your mainboard box, describes the features, specifications and performance of the motherboard and provides detailed information about the chipset.

**Chapter 2** begins with instructions on handling static-sensitive devices. Read this chapter when you want to install the processor and DIMM memory modules and when mounting the mainboard in the chassis. Also refer to this chapter to connect the floppy and hard disk drives, SCSI drives, the IDE interfaces, the parallel and serial ports, the keyboard and mouse, the power supply and various control panel buttons and indicators.

If you encounter any problems, see **Chapter 3**, which describes troubleshooting procedures for the video, the memory and the setup configuration stored in CMOS. For quick reference, a general FAQ [Frequently Asked Questions] section is provided.

**Chapter 4** includes an introduction to BIOS and provides detailed information on running the CMOS Setup utility.

Chapter 5 provides instructions on software, drivers and OS installation. Appendix A provides BIOS POST codes.

# **Table of Contents**

# Preface

| About This Manual   | iii |

|---------------------|-----|

| Manual Organization | iii |

# Chapter 1: Introduction

| 1-1 | Overview 1-1                                  |

|-----|-----------------------------------------------|

|     | Checklist 1-1                                 |

|     | Contacting Supermicro 1-2                     |

|     | Super i2DMR-8G2/i2DMR-iG2 Image 1-3           |

|     | Super i2DMR-8G2/i2DMR-iG2 Layout 1-4          |

|     | Super i2DMR-8G2/i2DMR-iG2 Quick Reference 1-5 |

|     | Motherboard Features1-6                       |

|     | Intel E7505 Chipset: System Block Diagram 1-9 |

| 1-2 | Chipset Overview 1-10                         |

| 1-3 | Special Features 1-11                         |

|     | Recovery from AC Power Loss 1-11              |

| 1-4 | PC Health Monitoring 1-11                     |

| 1-5 | ACPI Features 1-12                            |

| 1-6 | Power Supply 1-13                             |

| 1-7 | Super I/O1-13                                 |

|     |                                               |

# **Chapter 2: Installation**

| 2-1 | Static-Sensitive Devices 2-1                                   |

|-----|----------------------------------------------------------------|

|     | Precautions 2-1                                                |

|     | Unpacking 2-1                                                  |

| 2-2 | Itanium 2 Processor, Heatsink and Motherboard Installation 2-2 |

| 2-3 | Installing DIMMs 2-10                                          |

| 2-4 | I/O Ports/Control Panel Connectors 2-11                        |

| 2-5 | Connecting Cables 2-13                                         |

|     | EPS 12V Power Connector 2-13                                   |

|     | Processor VRM Power Connectors 2-13                            |

|     | Power Fail LED2-13                                             |

|     | NMI Button 2-13                                                |

|     | Power LED2-13                                                  |

|     | HDD LED 2-14                                                   |

|     | NIC1 LED 2-14                                                  |

|     | NIC2 LED 2-14                                                  |

|     | Overheat LED                                      | 2-14   |

|-----|---------------------------------------------------|--------|

|     | Reset Button                                      | 2-15   |

|     | Power Button                                      | 2-15   |

|     | Universal Serial Bus (USB0/1, USB2/3)             | 2-15   |

|     | Front Panel Universal Serial Bus Headers (USB4/5) | 2-16   |

|     | Serial Ports                                      | 2-16   |

|     | GLAN (Ethernet Port)                              | . 2-16 |

|     | Chassis Intrusion                                 | 2-16   |

|     | Fan Headers                                       | 2-17   |

|     | Speaker Header                                    | 2-17   |

|     | Wake-On-Ring                                      | . 2-17 |

|     | Power Fault Header                                | . 2-18 |

|     | SMB (System Management Bus)                       | . 2-18 |

|     | Alarm Reset                                       | . 2-18 |

|     | SMB_Power Connector                               | . 2-18 |

| 2-6 | Jumper Settings                                   | 2-19   |

|     | Explanation of Jumpers                            | 2-19   |

|     | GLAN Enable/Disable                               | 2-19   |

|     | CMOS Clear                                        | 2-19   |

|     | Watch Dog Enable/Disable                          | . 2-20 |

|     | VGA Enable/Disable                                | . 2-20 |

|     | SCSI Enable/Disable                               | . 2-20 |

|     | SCSI Termination Enable/Disable                   | . 2-20 |

|     | Force-Power-On Control                            | . 2-21 |

| 2-7 | Onboard Indicators                                | 2-21   |

|     | GLAN LEDs                                         | . 2-21 |

| 2-8 | Serial Port/Hard Disk Drive and SCSI Connections  | 2-22   |

|     | COM Port Connectors                               | 2-22   |

|     | IDE Connectors                                    | 2-22   |

|     | IPMI Connector                                    | 2-23   |

|     | Ultra 320 SCSI Connectors                         | 2-23   |

| Cha | pter 3: Troubleshooting                           |        |

| 3-1 | Troubleshooting Procedures              | 3-1 |

|-----|-----------------------------------------|-----|

|     | Before Power On                         | 3-1 |

|     | No Power                                | 3-1 |

|     | No Video                                | 3-2 |

|     | Memory Errors                           | 3-2 |

|     | Losing the System's Setup Configuration | 3-2 |

| 3-2 | Technical Support Procedures      | 3-2 |

|-----|-----------------------------------|-----|

| 3-3 | Frequently Asked Questions        | 3-3 |

| 3-4 | Returning Merchandise for Service | 3-4 |

# Chapter 4: BIOS

| 4-1 | Introduction          |  |

|-----|-----------------------|--|

| 4-2 | Main BIOS Setup       |  |

| 4-3 | Advanced Setup        |  |

| 4-4 | PCI/PnP Configuration |  |

| 4-5 | Security Setup        |  |

| 4-6 | Exit Options          |  |

|     |                       |  |

# Appendices:

| Appendix A: BIOS POST Codes A- | Codes A-1 |

|--------------------------------|-----------|

|--------------------------------|-----------|

# Chapter 1 Introduction

# 1-1 Overview

# Checklist

Congratulations on purchasing your computer motherboard from an acknowledged leader in the industry. Supermicro boards are designed with the utmost attention to detail to provide you with the highest standards in quality and performance.

Check that the following items have all been included with your motherboard. If anything listed here is damaged or missing, contact your retailer.

One (1) Supermicro Itanium2 Mainboard

One (1) ribbon cable for IDE devices (CBL-036)

One (1) heatsink retention(w/Mounting screws) (SKT-0147-RM-IT2)

Two (2) Power Pods (-VRM mechanism for the Itanium 2 CPUs) (VRM-0008)

One (1) Supermicro CD ROM

One (1) User's/BIOS Manual

# **Contacting Supermicro**

# Headquarters

| Address:  | SuperMicro Computer, Inc.                      |  |  |

|-----------|------------------------------------------------|--|--|

|           | 980 Rock Ave.                                  |  |  |

|           | San Jose, CA 95131 U.S.A.                      |  |  |

| Tel:      | +1 (408) 503-8000                              |  |  |

| Fax:      | +1 (408) 503-8008                              |  |  |

| Email:    | marketing@supermicro.com (General Information) |  |  |

|           | support@supermicro.com (Technical Support)     |  |  |

| Web Site: | www.supermicro.com                             |  |  |

# Europe

| Address:                                 | SuperMicro Computer B.V.                             |  |  |  |

|------------------------------------------|------------------------------------------------------|--|--|--|

|                                          | Het Sterrenbeeld 28, 5215 ML                         |  |  |  |

|                                          | 's-Hertogenbosch, The Netherlands                    |  |  |  |

| Tel:                                     | +31 (0) 73-6400390                                   |  |  |  |

| Fax:                                     | +31 (0) 73-6416525                                   |  |  |  |

| Email: sales@supermicro.nl (General Info |                                                      |  |  |  |

|                                          | <pre>support@supermicro.nl (Technical Support)</pre> |  |  |  |

|                                          | rma@supermicro.nl (RMA Dept.)                        |  |  |  |

# Asia-Pacific

| Address:           | SuperMicro, Taiwan                         |  |  |

|--------------------|--------------------------------------------|--|--|

|                    | D5, 4F, No. 16 Chien-Ba Road               |  |  |

|                    | Chung-Ho 235, Taipei Hsien, Taiwan, R.O.C. |  |  |

| Tel:               | +886-(2) 8226-3990                         |  |  |

| Fax:               | +886-(2) 8226-3991                         |  |  |

| Web Site:          | www.supermicro.com.tw                      |  |  |

| Technical Support: |                                            |  |  |

| Email:             | support@supermicro.com.tw                  |  |  |

| Tel:               | +886-2-8228-1366, ext.132 or 139           |  |  |

|                    |                                            |  |  |

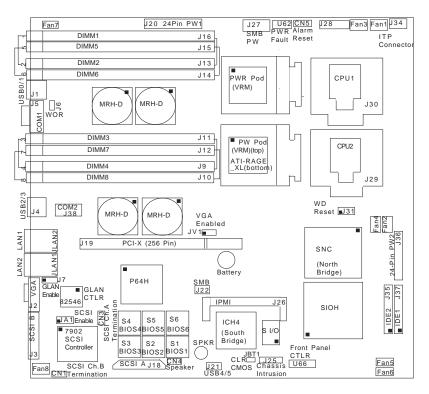

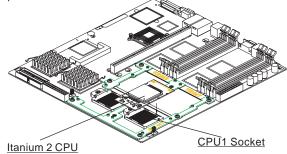

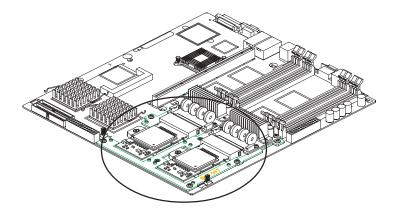

Figure 1-1. SUPER i2DMR-8G2/i2DMR-iG2 Image

<u>Note:</u> The difference between the i2DMR-8G2 and the i2DMR-iG2: There is Adaptec 7902 Ultra 320 SCSI on the i2DMR-8G2, and there is no SCSI on the i2DMR-iG2.

#### Figure 1-2. SUPER i2DMR-8G2/i2DMR-iG2 Motherboard Layout

(not drawn to scale)

# Notes:

1. Jumpers not noted are for testing purposes only.

2. " ■ " indicates the location of Pin 1.

3. For 1U servers, please use Fan1 and Fan2 for CPU cooling.

For 2U servers, please use Fan1, Fan2, Fan3 & Fan4 for CPU cooling.

4. The difference between the i2DMR-8G2 and the i2DMR-iG2: There is Adaptec 7902 Ultra 320 SCSI on the i2DMR-8G2, and there is no SCSI on the i2DMR-iG2.

**Warning:** The heatsink on the MRH-D chip has been pre-installed by the manufacturer. Please do not touch it. Turning the heatsink in a wrong way will damage it and will void the manufacturer's warranty.

# Quick Reference (i2DMR-8G2/i2DMR-iG2)

(\*Please refer to Chapter 2 for pin definitions and detailed information.)

| Jumper                                                            | Description                                                               |                                                | Default Setting    |  |

|-------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|--------------------|--|

| CN1, CN3                                                          | CN1, CN3 SCSI Cha.A(CN3)/Cha.B(CN1)Termination (*Note4)<br>Open (Enabled) |                                                |                    |  |

| J7                                                                | GLAN Enable/Disable                                                       |                                                | Pins 1-2 (Enabled) |  |

| J31                                                               | Watch D                                                                   | og                                             | Pins 1-2 (Reset)   |  |

| JBT1                                                              | CMOS C                                                                    | lear                                           | (*Note 4)          |  |

| JA1                                                               | SCSI Ena                                                                  | able/Disable (*Note5)                          | Pins 1-2 (Enabled) |  |

| JV1                                                               |                                                                           | able/Disable                                   | Pins 1-2 (Enabled) |  |

| <b>Connector</b>                                                  |                                                                           | <b>Description</b>                             |                    |  |

| Alarm Reset (                                                     | CN5)                                                                      | Fail Alarm Reset Switch                        |                    |  |

| BIOS#1-6 (S1-                                                     | -6)                                                                       | BIOS#1-6                                       |                    |  |

| Chassis Intrus                                                    | ion (J25)                                                                 | Chassis Intrusion Header                       |                    |  |

| COM1 (J5), C0                                                     | OM2 (J38)                                                                 | COM1 & COM2 Serial Port                        | and Header         |  |

| CPU1(J30), CF                                                     | PU2 (J29)                                                                 | CPU 1/2 Sockets                                |                    |  |

| DIMM#1-#8 (J                                                      | 9-J16)                                                                    | Memory (RAM) Slots:DIMM1                       | (J16),DIMM2 (J13), |  |

|                                                                   |                                                                           | DIMM3 (J11), DIMM4(J9), D                      | IMM5 (J15),        |  |

|                                                                   |                                                                           | DIMM6 (J14), DIMM7 (J12), DIMM8 (J10)(*Note 2) |                    |  |

| Fan Headers                                                       | (1-8)                                                                     | Fan1-Fan8 Headers.                             |                    |  |

| Front Panel C                                                     | TRL (U66)                                                                 | Front Control Panel Connec                     | ctor (*Note 3)     |  |

| IDE1 (J37), ID                                                    | E2 (J35)                                                                  | IDE1/2 Hard Disk Drive Cor                     | nnectors           |  |

| IPMI (J26)                                                        |                                                                           | IPMI 1.5, 2.0 Connector                        |                    |  |

| ITP (J34)                                                         |                                                                           | ITP Connector (For Testing Only)               |                    |  |

| PCI-X (J19)                                                       |                                                                           | PCI-X Bus 256-Pin Slot                         |                    |  |

| PWR1(J20), P                                                      | WR2(J36)                                                                  | Power1 and Power2 24-Pi                        | n-Connectors       |  |

| PWR Fault (U6                                                     | 62)                                                                       | Power Fault Connector                          |                    |  |

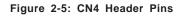

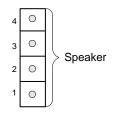

| Speaker (CN4                                                      | )                                                                         | Speaker Connector(*Note3)                      |                    |  |

| SMB (J22)                                                         |                                                                           | System Management Bus Connector                |                    |  |

| SMB_Power (                                                       | J27)                                                                      | System Management Bus Power Header             |                    |  |

| SCSI A&B (J1                                                      | 8,J3)                                                                     | SCSI A Connector(J18), SCSI B Connector(J3)    |                    |  |

|                                                                   |                                                                           | (*Note 4)                                      |                    |  |

| USB 0/1(J1),U                                                     | SB2/3(J4                                                                  | )Back Panel Universal Seria                    | I Ports            |  |

| USB4/5 (J21)                                                      |                                                                           | Front Panel USB Headers                        |                    |  |

| VGA Connected                                                     | or (J2)                                                                   | VGA Connector                                  |                    |  |

| WOR (J6)                                                          |                                                                           | Wake-on-Ring Header                            |                    |  |

| (*Notes: 1. For 1U servers, use Fan1&Fan2 for CPU cooling. For 2U |                                                                           |                                                |                    |  |

| servers, use Fan1, Fan2, Fan3, Fan4 for CPU cooling.              |                                                                           |                                                |                    |  |

| 2. See Chapter 2 for Memory Installation Instructions.            |                                                                           |                                                |                    |  |

| 3. See Chapte                                                     | er 2 for de                                                               | etailed information.                           |                    |  |

| 4. For i2DMR-8G2 only)                                            |                                                                           |                                                |                    |  |

# **Motherboard Features**

#### <u>CPU</u>

Two Intel Itanium 2 Processor sockets and power pod sites support: Single or dual Intel<sup>®</sup> Itanium 2<sup>™</sup> processors at a 400 MHz front side bus (system) speed up to 1.5 GHz, 6MB L3 Cache. (\*Notes: Please refer to the support section of our web site for a complete listing of supported processors (http:// www.supermicro.com/TECHSUPPORT/TechSupport.htm)

#### <u>Chipset</u>

- Intel E8870 chipset

- SNC-M(Scalable Node Controller) of the E8870 chipset

- SIOH (Server I/O Hub) of the E8870 chipset

- Four Memory Repeater Hubs-DDR(MRH-D) components of the E8870 chipset

- One P64H2 PCI-X bridge component

- Network Interface Controller (NIC) 10/100/1000 Ethernet controller that provides two GLAN ports

- One I/O Control Hub 4 (ICH 4) component:

- -6 USB ports (4 at the rear, 2 headers),

- -2 IDE bus routed through the flex cable to the peripheral board supporting one ATA100 master device

- 6-MB Flash using 6 Firmware Hub (FWH) components

#### Memory

Eight 184-pin DIMM sockets supporting up to 16 GB Registered ECC DDR-200 (PC1600) SDRAM (utilizing DDR266 operating at 200 MHz)

<u>Note</u>: 4-way Interleaved memory; requires at least 4 pieces of identical memory modules to be installed at the same time. See Section 2-3 for details.

#### Expansion Slots

\*For 1U Server:

• One 64-bit PCI-X 100 slot(\*For i2DMR-8G2), One 64-bit PCI-X 133 slot (\*For i2DMR-iG2)

\*For 2U servers: it can support up to 3 PCI-X slots:

• One 64-bit PCI-X 100 slot(\*For i2DMR-8G2), One 64-bit PCI-X 133 slot (\*For i2DMR-iG2)

• Two 64-bit PCI-X 133 slots

#### BIOS

- 6-MB AMI® Flash BIOS (total of 6 BIOS chips)

- PCI 2.2, BIOS chips, Plug and Play (PnP), SMBIOS 2.3

- ACPI (limited)

#### PC Health Monitoring

- · Onboard voltage monitors for CPU cores, system voltages

- · Fan status monitor with firmware/software on/off Speed control

- CPU/chassis temperature monitors

- CPU fan speed control

- · CPU slow-down on temperature overheat

- CPU thermal trip support for processor protection, +5V standby alert LED

- · Power-up mode control for recovery from AC power loss

- Auto-switching for VRMs

- System overheat LED and control

- Chassis intrusion detection

#### Thermal Control

- Overheat LED Indication

- Thermal control

- 8 Fan connectors

#### ACPI Features

- Internal/external modem ring-On

- · Control of power-on mode for recovery of power loss

- · CPU thermal trip support for processor protection

- · Main switch override mechanism

#### <u>Onboard I/O</u>

- Adaptec 7902 Dual Channel Ultra 320 SCSI (\*i2DMR-8G2 only)

- One IPMI 1.5 & 2.0 socket

- One Intel 82546 Gigabit Ethernet controller which supports two GLAN

ports

- Onboard ATI Rage XL 8MB PCI Graphic Control

- Super I/O (W83627)

- Winbond Hardware Monitoring IC (W82791)

- Low Pin Count(LPC) Super I/O with one external serial port and an internal header supporting 2 Fast UART 16550A compatible serial ports

- Dual ATA100 channels

• Up to 6 USB 2.0 (4 ports and 2 headers)

#### Other

- Internal/external modem ring-on

- Console redirection

- · Watch Dog & Supero DoctorIII for system manageability

- In-Target Probe (ITP) port

- Joint Test Action Group (JTAG)/boundary scan support through ITP or external source

- Core ratio programming via the SNC-M

- Clock Buffering

- Embedded D2D converters

- I<sup>2</sup> C Logic: Includes:

- -Field Replacement Unit (FRU) device ID that is accessed through a private  $\ensuremath{I^2\,C}$  bus

- -Temperature sensors

#### CD ROM

· BIOS flash upgrade utility and device drivers

#### **Dimensions**

• ATX Ext. 12.25" x 13.05" (311.2mm x 331.5 mm)

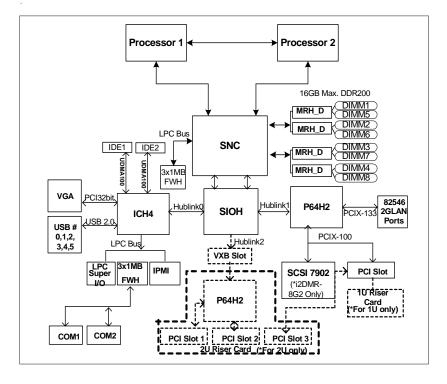

#### Figure 1-9. Block Diagram of the i2DMR-8G2/i2DMR-iG2 Motherboard

**Note:** This is a general block diagram. Please see the previous Motherboard Features pages for details on the features of the motherboard.

# 1-2 Chipset Overview

Built upon the functionality and the capability of the Intel E8870 (870) chipset, the i2DMR-8G2/i2DMR-iG2 motherboard provides the performance and feature set required for high-end server platforms with configuration options optimized for communications, presentation, storage, computation or database applications. The Intel E8870 chipset consists of the following four primary components: the Scalable Node Controller (SNC), Server I/O Hub (SIOH), the Memory Repeater Hub for Synchronous Double Data Rate Memory(MRH\_D) and Scalability Port Switch (SPS) (\*Note Below). Complementary components include the I/O Hub Controller (Intel ICH4), the Firmware Hub (FWH), and the PCI Bus Bridge (P64H2).

#### The major bus groups are:

<u>Processor system bus</u>: supporting up to two processors and one Scalable Node Controller (SNC), with a maximum operating frequency of 200 MHz@400 MT/s.

<u>Rambus and SNC Interface</u>: the Interconnection between the SNC and Memory Repeater Hub (MRH-D), operating at a maximum frequency of 400 MHz.

<u>Synchronous DDR Interface</u>: interface between the MRH-D and up to four DIMM sockets, operating at the operating clock frequency of 100 MHz per branch channel.

<u>Scalability Port (SP) Interface</u>: a 400MHz, double-pumped, simultaneous bidirectional signaling (SBD) interface.

<u>Hub Interface 2.0</u>: interface between the SIOH and the P64H2 using 266 MHz strobes on a 16-bit wide data bus.

<u>Hub Interface 1.5</u>: interface between the SIOH and the ICH4 using 133 MHz strobes on a 8-bit wide data bus.

Local Firmware Hub (LPC): Interface between the SNC and local firmware.

<u>System Management Bus (SMBus)</u>: a subset of the I<sup>2</sup>C serial bus integrated into the SNC, SPS, and SIOH.

(\*Note: The Scalability Port Switch-SPS is not used in the i2DMR-8G2/iG2.)

# **Complementary Components include:**

# I/O Controller Hub (ICH4)

The ICH4 is the fourth-generation I/O Controller Hub subsystem that integrates many of the input/output functions of the chipset, including a twochannel ATA100 Bus Master IDE controller. The ICH4 also interfaces with PCI and various communications ports. Nearly all communications between the GMCH and the ICH4 takes place over the hub Interface, which is a 66 MHz/266 MB/s bus.

# P64H2 PCI-X Hub (P64H2)

The P64H2 PCI-X Hub provides a 16-bit connection to the MCH for high-performance I/O capability and two 64-bit PCI-X interfaces.

# **1-3 Special Features**

# Recovery from AC Power Loss

BIOS provides a setting for you to determine how the system will respond when AC power is lost and then restored to the system. You can choose for the system to remain powered off (in which case you must hit the power switch to turn it back on) or for it to automatically return to a poweron state. See the Power Lost Control setting in the Advanced BIOS Setup section (Peripheral Device Configuration) to change this setting. The default setting is Last State.

# **1-4 PC Health Monitoring**

This section describes the PC health monitoring features of the SUPER i2DMR-8G2/i2DMR-iG2. All have an onboard System Hardware Monitor chip that supports PC health monitoring.

# Fan Status Monitor with Firmware/Software On/Off Control

The PC health monitor can check the RPM status of the cooling fans. The onboard 3-pin chassis fans are controlled by the power management functions.

# **CPU Overheat LED and Control**

This feature is available when the user enables the CPU overheat warning function in the BIOS. This allows the user to define an overheat temperature. When this temperature is exceeded, fans will speed up, and the warning LED is triggered.

# Auto-Switching Voltage Regulator for the CPU Core

The auto-switching voltage regulator for the CPU core can support up to 20A current and auto-sense voltage IDs ranging from 1.1V to 1.5V (\*supported by VRMs only). This will allow the regulator to run cooler and thus make the system more stable.

# **1-5 ACPI Features**

# External Modem Ring-On

Wake-up events can be triggered by a device such as the external modem ringing when the system is in the SoftOff state. Note that external modem ring-on can only be used with an SSI compliant power supply.

# 1-6 Power Supply

As with all computer products, a stable power source is necessary for proper and reliable operation. It is even more important for processors that have high CPU clock rates.

The SUPER i2DMR-8G2/i2DMR-iG2 requires a 24-pin connector and two 4pin 12V/15A connectors for CPU VRMs. Although most power supplies generally meet the specifications required by the CPU, some are inadequate. You should use one that will supply at least 500W of power, and an even higher wattage power supply is recommended for high-load configurations. Also your power supply must supply 2A for the Ethernet ports and the E8870 chipset.

It is strongly recommended that you use a high quality power supply that meets SSI EPS 12V 1U 500W PS Specification. To verify the status of SSI compliance, please visit the web site at http://www.ssiforum.org/. Additionally, in areas where noisy power transmission is present, you may choose to install a line filter to shield the computer from noise. It is recom-

mended that you also install a power surge protector to help avoid problems caused by power surges.

# 1-7 Super I/O

The disk drive adapter functions of the Super I/O provides two high-speed, 16550 compatible serial communication ports (UARTs). Each UART includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete modem control capability and a processor interrupt system. Both UARTs provide legacy speed with baud rate of up to 115.2 Kbps as well as an advanced speed with baud rates of 250 K, 500 K, or 1 Mb/s, which support higher speed modems.

## Notes

# Chapter 2 Installation

# 2-1 Static-Sensitive Devices

Electric-Static-Discharge (ESD) can damage electronic components. To prevent damage to your system board, it is important to handle it very carefully. The following measures are generally sufficient to protect your equipment from ESD.

# Precautions

- Use a grounded wrist strap designed to prevent static discharge.

- Touch a grounded metal object before removing the board from the antistatic bag.

- Handle the board by its edges only; do not touch its components, peripheral chips, memory modules or gold contacts.

- When handling chips or modules, avoid touching their pins.

- Put the motherboard and peripherals back into their antistatic bags when not in use.

- For grounding purposes, make sure your computer chassis provides excellent conductivity between the power supply, the case, the mounting fasteners and the motherboard.

# Unpacking

The motherboard is shipped in antistatic packaging to avoid static damage. When unpacking the board, make sure the person handling it is static protected.

# 2-2 Itanium2 Processor and Heatsink Installation

When handling the processor package, avoid placing direct pressure on the label area of the fan. Also, do not place the motherboard on a conductive surface, which can damage the BIOS battery and prevent the system from booting up.

**IMPORTANT:** Always connect the power cord last and always remove it before adding, removing or changing any hardware components. Make sure that you install the processor into the CPU socket **before** you install the CPU heat sink.

**Note:** To optimize the functionality and capability of the i2DMR-8G2/ i2DMR-iG2, we recommend that i2DMR-8G2/i2DMR-iG2 be installed in Supermicro chassis only.

**Warning:** The heatsink on the MRH-D chip has been pre-installed by the manufacturer. Please do not touch it. Turning the heatsink in a wrong way will damage it and will void the manufacturer's warranty.

# A. Locating the components included in the shipping package

Locate the following components, which are included in the shipping package.

Two (2) Power Pod (VRM-0008) Two (2) Itanium 2 Heatsinks (SNK-0046)(\*not included; sold separately) One Package of Retention Mechanism, including:

One (1) Retention Mechanism (SKT-0147-RM-IT2) Eight (8) M3 5mm Screws Three (3) 6-32 4.5mm Screws Six (6) 6-32 8mm Screws One (1) M2.5 Hex Key (\*for CPU removal and locking)

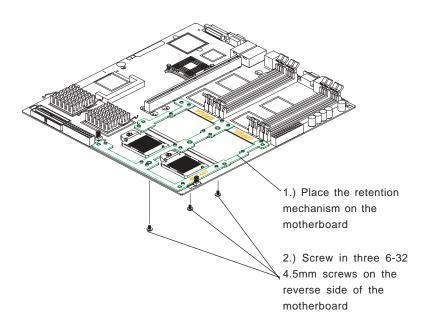

## **B. Installing the Heatsink Retention Mechanism on the Motherboard**

1. Place the retention mechanism (P/N SKT-0147-RM-IT2) on the motherboard as shown in the picture below:

2. Secure the retention mechanism onto the motherboard by screwing three (3) 6-32 4.5MM screws into the mounting holes on the back of the motherboard.

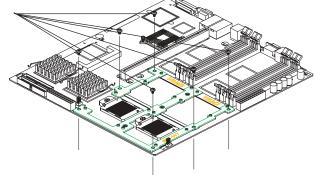

# C. Installing Motherboard into chassis

\*Note: <u>To optimize the functionality and the capability of the i2DMR-8G2/</u> i2DMR-iG2, we strongly recommend that the i2DMR-8G2/i2DMR-iG2 be installed in Supermicro's proprietary chassis only-the SC813HS-500W (\*for 1 U), SC823HS-500W (\*for 2U).

1. Locate six(6) 6-32 8mm screws in the retention mechanism shipping package.

2. On the retention mechanism located on the motherboard, locate the six mounting holes (as shown in the picture below), and locate their six corresponding mounting holes in the chassis.

3. Align the six mounting holes on the motherboard against the corresponding mounting holes in the chassis.

4. Screw six (6) 6-32 <u>8mm</u> screws into the mounting holes on the retention mechanism and the mounting holes in the chassis as shown in the pictures below.

5. Locate six 6-32 4.5mm screws included in the chassis mounting kit. Secure the motherboard onto the chassis by screwing 6-32 4.5mm screws into all the remaining mounting holes on the motherboard and the mounting holes in the chassis.

1.) Screw six 6-32 8mm screws into mounting holes on the board and on the chassis.

Secure the motherboard onto the chassis by screwing

4.5mm screws into all the remaining mounting holes on the board and on the chassis.

# D. Installing and securing the Itanium 2 CPU onto the motherboard

1. Insert the Itanium 2 CPU into the CPU1 Socket. Make sure that CPU Pin 1 is aligned with the cut angle of the CPU socket. <u>(\*See Note)</u> as shown in the picture below:

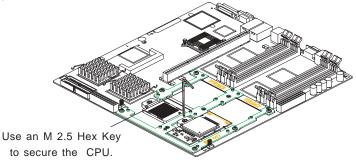

2. Use an M2.5 Hex Key to secure the Itanium 2 CPU as shown in the picture below:

3. Repeat Step 1 and Step 2 to install the second Itanium2 CPU as needed. (\*See Note)

(\*Notes: Please refer to Chapter 1 Page 1-4 for the locations of CPU1 Socket and CPU2 Socket.)

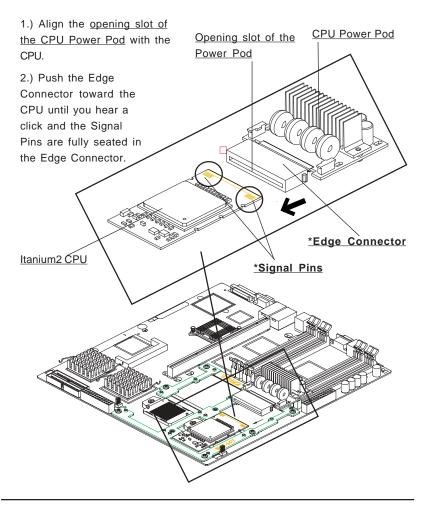

## E. Installing and securing the Power Pod onto the Itanium 2 CPU

(\*Notes: <u>1.The CPU Power Pod is a VRM mechanism specially designed</u> for the Itanium 2 processors.)

1. Locate the opening slot on the CPU Power Pod, and align the opening slot with the Itanium2 CPU installed on the motherboard.

2. Carefully push the Edge Connector of the Power Pod toward the CPU until the Signal Pins on both edges of the CPU are fully seated in the Edge Connector and you hear a click. (\*Warning: Unless the Signal Pins of the CPU are fully seated in the Edge Connector of the Power Pod, the CPU will not function correctly!!)

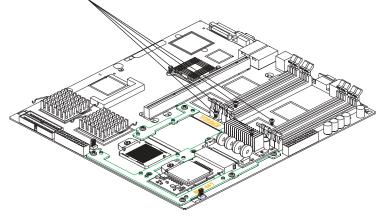

3. Locate four(4) M3 screws in the VRM-008 package. Secure the Power Pod onto the motherboard with four(4) M3 screws as shown in the picture below:

3.) Secure the Power Pod onto the motherboard with four(4) M3 screws.

4. Repeat Step 1 and Step 2 to install the second Itanium2 CPU (w/Power Pod) as needed.

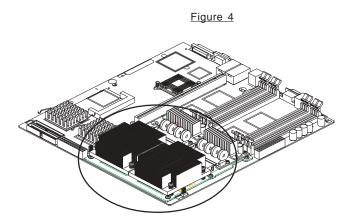

Dual Itanium 2 Processors (w/ Power Pods installed)

# F. Installing the Heatsink on the CPU(\*for CPU w/o Heatsink only)

(\*Warning: <u>Do not apply any thermal grease to the heatsink-the required</u> <u>amount of thermal grease has already been applied.</u>)

(\*Note: <u>To maximizing the cooling effect of the i2DMR-8G2/iG2, we</u> strongly recommend that Supermicro's proprietary heatsinks (SNK-046) be used with the Itanium 2 CPUs.)

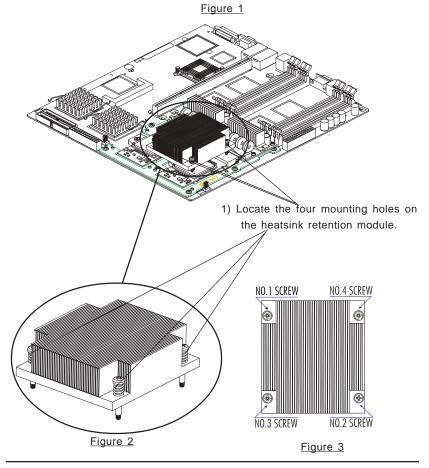

1. Place the heatsink (P/N SKT-0046) on top of the CPU so that the four mounting holes are aligned with those on the retention mechanism as shown in Figure 1 below.

2. Screw in two diagonal screws (ie the #1 and #2 screws) until just snug (do not fully tighten), then do the same with the remaining diagonal screws as shown in Figure 2 and Figure 3.

3. Secure the heatsink onto the CPU by tightening all four screws as shown in Figure 3.

4. Repeat the above steps 1-3 to install the second heatsink on the second CPU if needed as shown in the Figure 4.

The i2DMR-8G2/iG2 with two heatsinks installed

# G. Connecting AC Power to the motherboard and the Power Pods

1. Connect the 24-pin power connector from the AC Power Supply to the motherboard. (Refer to Page 1-4 for the locations of power connectors.)

2. Connect two(2) 4-pin 12V/15A power connectors from the AC Power Supply to the power pods.

# 2-3 Installing DIMMs

**Note:** Check the Supermicro web site for recommended memory modules: http://www.supermicro.com/TECHSUPPORT/FAQs/Memory\_vendors.htm

# CAUTION

Exercise extreme care when installing or removing DIMM modules to prevent any possible damage. Also note that the memory is interleaved to improve performance (see step 1).

#### **DIMM Installation**

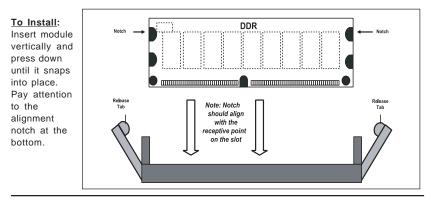

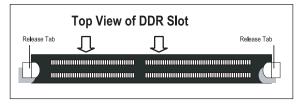

- Insert either 4 or 8 identical DIMMs (-Memory of the same size and type) into the memory slots, starting with DIMM1(J16), DIMM2(J13), DIMM3(J11) & DIMM4(J9). (DIMM1-DIMM4 are the DIMM sockets colored in blue.) If four more DIMMs are used, insert DIMM5(J15), DIMM6(J14), DIMM7(J12) and DIMM8(J10) into the slots. (DIMM5-DIMM8 are the DIMM sockets colored in black.) The memory scheme is interleaved, and <u>you</u> <u>must install four modules at a time</u>, beginning with DIMM1, DIMM2, DIMM3, DIMM4 (blue slots).

- Insert each DIMM module vertically into its slot. Pay attention to the notch along the bottom of the module to prevent inserting the DIMM module incorrectly.

- Gently press down on the DIMM module until it snaps into place in the slot. Repeat for all modules (see step 1 above).

#### Memory Support

The i2DMR-8G2/i2DMR-iG2 supports up to 16 GB of buffered, Reg. ECC DDR-200 (utilizing DDR 266 memory operating at DDR 200). All motherboards were designed to support 2 GB modules in each slot.

Figure 2-2. Installing and Removing DIMMs

#### To Remove:

Use your thumbs to gently push near the edge of both ends of the module. This should release it from the slot.

# 2-4 I/OPorts/Control Panel Connectors

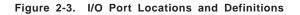

The I/O ports are color coded in conformance with the PC 99 specification. See Figure 2-3 below for the colors and locations of the various I/O ports.

USB Ports COM Port

(\*For i2DMR-8G2 only)

External SCS

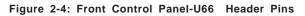

# Front Control Panel (U66)

U66 contains header pins for various buttons and indicators that are normally located on a control panel at the front of the chassis. These connectors are designed specifically for use with Supermicro server chassis. See the figure below for the descriptions of the various control panel buttons and LED indicators. Refer to the following section for descriptions and pin definitions.

# Speaker Connector (CN4)

CN4 contains header pins for the Speaker Header located at the front of the chassis. (\*See the Connector Section for details.)

# 2-5 Connecting Cables EPS 12V Power

Connector

There are two 24-pin main power supply connector(J20, J36) on the i2DMR-8G2/i2DMR-iG2. These power connectors meet the SSI EPS 12V specification. (\*Only one main power supply is needed.) See the table on the right for pin definitions.

#### Processor Power Connectors

In addition to the primary SSI EPS12V 24-pin power connectors (above), there are also two 4-pin EPS 12V/15A power connectors to be connected to CPU Power Pods (VRMs). Refer to the table on the right for pin definitions.

# Power Fail LED

The Power Fail LED connection is located on pins 5 and 6 of U66. Refer to the table on the right for pin definitions.

#### **NMI** Button

The non-maskable interrupt button header is located on pins 19 and 20 of U66. Refer to the table on the right for pin definitions.

# Power LED

The Power LED connection is located on pins 15 and 16 of U66. Refer to the table on the right for pin definitions.

EPS 12V Power Supply 24-pin Connectors: J20,J36--Pin Definitions

| Pin Number Definition |         | Pin Number Definition |        |

|-----------------------|---------|-----------------------|--------|

| 13                    | +3.3V   | 1                     | +3.3V  |

| 14                    | -12V    | 2                     | +3.3V  |

| 15                    | COM     | 3                     | COM    |

| 16                    | PS_ON#  | 4                     | +5V    |

| 17                    | COM     | 5                     | COM    |

| 18                    | COM     | 6                     | +5V    |

| 19                    | COM     | 7                     | COM    |

| 20                    | Res(NC) | 8                     | PWR_OK |

| 21                    | +5V     | 9                     | 5VSB   |

| 22                    | +5V     | 10                    | +12V   |

| 23                    | +5V     | 11                    | +12V   |

| 24                    | COM     | 12                    | +3.3V  |

#### EPS 12V Power Supply 4-pin Connectors: Pin Definitions

| Pin               | Pin  |      |               |

|-------------------|------|------|---------------|

| Number Definition |      | Numb | er Definition |

| 1                 | Thru | 2    | Ground        |

| 3                 | Thru | 4    | +12V          |

| Power Fail LED Pin<br>Definitions<br>(U66) |            |  |

|--------------------------------------------|------------|--|

| Pin<br>Number                              | Definition |  |

| 5                                          | Vcc        |  |

| 6                                          | GND        |  |

| NMI Button Pin    |            |  |

|-------------------|------------|--|

| Definitions (U66) |            |  |

| Pin               |            |  |

| Number            | Definition |  |

|                   |            |  |

| Number | Definition |

|--------|------------|

| 19     | Control    |

| 20     | Ground     |

PWR\_LED Pin Definitions

| (U66)  |            |  |

|--------|------------|--|

| Pin    |            |  |

| Number | Definition |  |

| 15     | Vcc        |  |

| 16     | Control    |  |

#### HDD LED

The HDD LED connection is located on pins 13 and 14 of U66. Attach the hard drive LED cable here to display disk activity (for any hard drives on the system, including SCSI, Serial ATA and IDE). See the table on the right for pin definitions.

## NIC1 LED

The NIC (Network Interface Controller) LED connection for the GLAN port is located on pins 11 and 12 of U66. Attach the NIC LED cable to display network activity. Refer to the table on the right for pin definitions.

#### NIC2 LED

The NIC (Network Interface Controller) LED connection for the GLAN port is located on pins 9 and 10 of U66. Attach the NIC LED cable to display network activity. Refer to the table on the right for pin definitions.

# Overheat LED (OH)

Connect an LED to the OH connection on pins 7 and 8 of U66 to provide advanced warning of chassis overheating. Refer to the table on the right for pin definitions.

#### HDD LED Pin Definitions

| (U66)  |            |  |

|--------|------------|--|

| Pin    |            |  |

| Number | Definition |  |

| 13     | Vcc        |  |

| 14     | HD Active  |  |

| NIC L       | ED Pin |  |

|-------------|--------|--|

| Definitions |        |  |

| (L          | J66)   |  |

| Pin         |        |  |

| Pin    |            |

|--------|------------|

| Number | Definition |

| 11     | Vcc        |

| 12     | GND        |

|        |            |

NIC 2 LED Pin Definitions (U66) Pin Number Definition 9 Vcc 10 GND

| Overheat (OH) LED<br>Pin Definitions<br>(U66) |            |  |

|-----------------------------------------------|------------|--|

| Pin<br>Number                                 | Definition |  |

| 7<br>8                                        | Vcc<br>GND |  |

#### **Reset Button**

The Reset Button connection is located on pins 3 and 4 of U66. Attach it to the hardware reset switch on the computer case. Refer to the table on the right for pin definitions.

## **Power Button**

The Power Button connection is located on pins 1 and 2 of U66. Momentarily contacting both pins will power on/off the system. This button can also be configured to function as a suspend button (with a setting in BIOS - see Chapter 4). To turn off the power when set to suspend mode, depress the button for at least 4 seconds. Refer to the table on the right for pin definitions.

| Reset Pin<br>Definitions<br>(U66) |            |  |

|-----------------------------------|------------|--|

| Pin                               |            |  |

| Number                            | Definition |  |

| 3                                 | Reset      |  |

| 4                                 | Ground     |  |

| Power Button<br>Connector<br>Pin Definitions<br>(JF2) |            |

|-------------------------------------------------------|------------|

| Pin                                                   |            |

| Number                                                | Definition |

| 1                                                     | PW_ON      |

| 2                                                     | Ground     |

# Universal Serial Bus (USB0/1, USB2/3)

Two USB 2.0 ports:USB0/1 (J1) and USB2/3 (J4) are located on the back panel. USB0 is the bottom connector and USB1 is the top connector of J1. USB2 is the bottom connector and USB3 is the top connector of J4. See the table on the right for pin definitions.

| Universal Serial B | us Pin Definitions |

|--------------------|--------------------|

| USB0(J1), USB2(J4) | USB1(J1), USB3(J4) |

| Pin    |            | Pin    |            |

|--------|------------|--------|------------|

| Number | Definition | Number | Definition |

| 1      | +5V        | 1      | +5V        |

| 2      | P0-        | 2      | P0-        |

| 3      | P0+        | 3      | P0+        |

| 4      | Ground     | 4      | Ground     |

| 5      | N/A        | 5      | Key        |

# Front Panel Universal Serial Bus Header

Two extra USB headers (USB4/ USB5) (J21) can be used for front side USB access. You will need a USB cable to use either connection. Refer to the tables on the right for pin definitions.

#### Front Panel Universal Serial Bus(J21) Pin Definitions

|--|

| Pin    |            |

|--------|------------|

| Number | Definition |

| 1      | +5V        |

| 2      | P0-        |

| 3      | P0+        |

| 4      | Ground     |

| 5      | Key        |

## **Serial Ports**

There are two Serial Ports on the i2DMR-8G2/i2DMR-iG2 The COM1 serial port (J5) is located under the parallel port (see Figure 2-3) and the COM2 header (J38) is located next to the GLAN1 port. See the tables on the right for pin definitions.

# GLAN Ports (Ethernet Ports)

Two G-bit Ethernet ports (designated LAN1, LAN2) are located between Keyboard/Mouse connectors and the VGA connector. This port accepts RJ45 type cables.

# **Chassis Intrusion**

A Chassis Intrusion header (J25) is located below the S I/O chip. Attach the appropriate cable to inform you of a chassis intrusion. See the tables on the right for pin definitions.

Serial Ports Pin Definitions (COM1-J5, COM2-J38)

|            | (,         | · · · · · , |            |

|------------|------------|-------------|------------|

| Pin Number | Definition | Pin Number  | Definition |

| 1          | DCD        | 6           | DSR        |

| 2          | Serial In  | 7           | RTS        |

| 3          | Serial Out | 8           | CTS        |

| 4          | DTR        | 9           | RI         |

| 5          | Ground     |             |            |

|            |            |             |            |

| Chassis Intrusion<br>Pin Definitions<br>(J25) |            |

|-----------------------------------------------|------------|

| Pin                                           |            |

| Number                                        | Definition |

| 1                                             | Instrusion |

| 2                                             | Ground     |

### **Fan Headers**

The i2DMR-8G2/i2DMR-iG2 has eight fan headers. See the table on the right for pin definitions.

| Pin                         |                |

|-----------------------------|----------------|

| Number                      | Definition     |

| 1                           | Ground (black) |

| 2                           | +12V (red)     |

| 3                           | Tachometer     |

| Caution: Fan headers are DC |                |

Fan Header Pin Definitions

power.

## Speaker Header

The Speaker header is located on CN4. See the table on the right for speaker pin definitions. <u>Note</u>: The speaker connector pins are for use with an external speaker. If you wish to use the onboard speaker, you should close pins 3, and 4 with a jumper to enable it.

## Wake-On-Ring

The Wake-On-Ring header is designated JWOR(J6). This function allows your computer to receive and "wake-up" by an incoming call to the modem when in suspend state. See the table on the right for pin definitions. You must have a Wake-On-Ring card and cable to use this feature.

| Wa  | ke-on-Ring  |

|-----|-------------|

| Pin | Definitions |

| (.  | IWOR-J6)    |

| Pin    |            |

|--------|------------|

| Number | Definition |

| 1      | Ground     |

| 2      | Wake-up    |

#### **Power Fault**

Connect a cable from your power supply to the U62 header to provide warning of power supply failure. This warning signal is passed through the PWR\_LED pin on U66 to indicate of a power failure on the chassis. See the table on the right for pin definitions.

#### SMB

A System Management Bus header is located at J22. Connect the appropriate cable here to utilize SMB on your system.

#### Alarm Reset

The system will notify you in the event of a power supply failure. This feature assumes that Supermicro redundant power supply units are installed in the chassis. If you only have a single power supply installed, you should disable this (the default setting) with (CN5) to prevent false alarms. See the table on the right for jumper settings. (The Alarm Reset header is located next to the PWR Fault header and close to Fan3.)

#### SMB Power (I<sup>2</sup> C) Connector

I<sup>2</sup> C Connector (J27), located between the PWR ForceOn Header and the PWR Fault header, monitors the status of PWR Supply, Fan and system temperature.

| Power Fault<br>Pin Definitions (U62) |  |  |

|--------------------------------------|--|--|

| Definition                           |  |  |

|                                      |  |  |

| P/S 1 Fail Signal                    |  |  |

| P/S 2 Fail Signal                    |  |  |

| P/S 3 Fail Signal                    |  |  |

| Reset (from MB)                      |  |  |

|                                      |  |  |

**Note:** This feature is only available when using redundant Supermicro power supplies.

SMB Header Pin Definitions (J22)

| Pin    |               |

|--------|---------------|

| Number | Definition    |

| 1      | Data          |

| 2      | Ground        |

| 3      | Clock         |

| 4      | No Connection |

Alarm Reset Jumper Settings (CN5)

|          | ()         |

|----------|------------|

| Jumper   |            |

| Position | Definition |

| Open     | Enabled    |

| Closed   | Disabled   |

SMB PWR Pin Definitions (J27)

| Pin # | Definition |

|-------|------------|

| 1     | Clock      |

| 2     | Data       |

| 3     | N/A        |

| 4     | N/A        |

| 5     | N/A        |

# 2-6 Jumper Settings

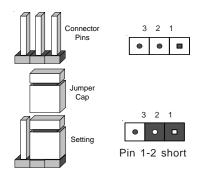

## Explanation of Jumpers

To modify the operation of the motherboard, jumpers can be used to choose between optional settings. Jumpers create shorts between two pins to change the function of the connector. Pin 1 is identified with a square solder pad on the printed circuit board. See the motherboard layout pages for jumper locations.

**Note:** On two pin jumpers, "Closed" means the jumper is on and "Open" means the jumper is off the pins.

## **GLAN Enable/Disable**

J7 enables or disables the GLAN port(s) on the motherboard. See the table on the right for jumper settings. The default setting is enabled.

#### **CMOS** Clear

JBT1 is not literally a jumper but consists of two contact pads. To clear the contents of CMOS, short these pads together by touching them both with a metal conductor such as the head of a small screwdriver. JBT1 is located between the FPUSB4/5(J21) and Chassis Intrusion(J25) headers on the motherboard. For ATX/SSI power supplies, you must completely shut down the system and remove the AC power cord before clearing CMOS.

| GLAN            |

|-----------------|

| Enable/Disable  |

| Jumper Settings |

| . (J7)          |

| Jumper   |            |

|----------|------------|

| Position | Definition |

| Pins 1-2 | Enabled    |

| Pins 2-3 | Disabled   |

#### Watch Dog

J31 controls Watch Dog, a system monitor that takes action when a software application freezes the system. Pins 1-2 will have WD reset the system if a program freezes. Pins 2-3 will generate a non-maskable interrupt for the program that has frozen (requires software implementation). Watch Dog must also be enabled in BIOS.

#### VGA Enable/Disable

JV1 allows you to enable or disable the VGA port. The default position is on pins 1 and 2 to enable VGA. See the table on the right for jumper settings.

#### SCSI Enable/Disable (\*i2DMR-8G2 only)

The SCSI jumper at JA1 allows you to enable or disable the onboard SCSI controller. The normal (default) position is on pins 1-2 to enable SCSI termination. See the table on the right for jumper settings.

#### SCSI Termination Enable/ Disable (\*i2DMR-8G2 only)

Jumpers CN1 and CN3 allow you to enable or disable termination for the SCSI connectors. Jumper CN3 controls SCSI channel A and CN1 is for SCSI channel B. The default setting is open to enable (terminate) both SCSI channels. See the table on the right for jumper settings.

| Watch Dog       |       |

|-----------------|-------|

| Jumper Settings | (J31) |

| Jumper   |             |

|----------|-------------|

| Position | Definition  |

| Pins 1-2 | WD to Reset |

| Pins 2-3 | WD to NMI   |

| Open     | Disabled    |

VGA Enable/Disable Jumper Settings

| (JV1)    |                  |  |

|----------|------------------|--|

| Jumper   |                  |  |

| Position | Definition       |  |

| 1-2      | Enabled(default) |  |

| 2-3      | Disabled         |  |

|          |                  |  |

SCSI Enable/Disable Jumper Settings (JA1)

| ()         |  |  |

|------------|--|--|

|            |  |  |

| Definition |  |  |

| Enabled    |  |  |

| Disabled   |  |  |

|            |  |  |

| SCSI Channel Termination |

|--------------------------|

| Enable/Disable           |

| Jumper Settings          |

| (CN1, CN3)               |

| Jumper<br>Position | Definition          |

|--------------------|---------------------|

| Open<br>Closed     | Enabled<br>Disabled |

## Force-Power-On Enable/ Disable

Jumper J23, located next to the 24-Pin power connector, allows you to enable or disable the function of Force-Power-On. If enabled, the power will always stay on automatically. If this function disabled, the user needs to press the power button to power on the system.

| Force Power On<br>(J23) |            |  |

|-------------------------|------------|--|

| Jumper                  |            |  |

| Position                | Definition |  |

| Off                     | Normal     |  |

Force On

On

# 2-7 Onboard Indicators

#### **GLAN LEDs**

Each of the Gigabit Ethernet LAN ports (located beside the COM2 port) has two LEDs. The yellow LED indicates activity while the other LED may be green, orange or off to indicate the speed of the connection. See the table at right for the functions associated with the second LED.

#### 1 Gb LAN Right LED Indicator

| LED    |               |

|--------|---------------|

| Color  | Definition    |

| Off    | No Connection |

| Green  | 100 Mb        |

| Orange | 1 Gb          |

# 2-8 COM Port, IDE, IPMI and SCSI Connections

Note the following when connecting the hard disk drive cable:

• A red mark on a wire typically designates the location of pin 1.

### COM Port 1 (J5) & COM 2 Header (J38)

The COM Port 1 is located on J5, and the COM 2 Header is located on J38.

## **IDE Connectors**

There are no jumpers to configure the onboard IDE#1 and #2 connectors (at J37 and J35, respectively). See the table on the right for pin definitions.

| (000, 007) |               |            |                |

|------------|---------------|------------|----------------|

| Pin Number | Function      | Pin Number | Function       |

| 1          | Reset IDE     | 2          | GND            |

| 3          | Host Data 7   | 4          | Host Data 8    |

| 5          | Host Data 6   | 6          | Host Data 9    |

| 7          | Host Data 5   | 8          | Host Data 10   |

| 9          | Host Data 4   | 10         | Host Data 11   |

| 11         | Host Data 3   | 12         | Host Data 12   |

| 13         | Host Data 2   | 14         | Host Data 13   |

| 15         | Host Data 1   | 16         | Host Data 14   |

| 17         | Host Data 0   | 18         | Host Data 15   |

| 19         | GND           | 20         | Key            |

| 21         | DRQ3          | 22         | GND            |

| 23         | I/O W rite-   | 24         | GND            |

| 25         | I/O Read-     | 26         | GND            |

| 27         | IOCHRDY       | 28         | BALE           |

| 29         | DACK3-        | 30         | GND            |

| 31         | IRQ14         | 32         | IOCS16-        |

| 33         | Addr 1        | 34         | GND            |

| 35         | Addr 0        | 36         | Addr 2         |

| 37         | Chip Select 0 | 38         | Chip Select 1- |

| 39         | Activity      | 40         | GND            |

IDE Connector Pin Definitions (J35, J37)

### IPMI

J26 is designated as the IPMI Socket for the i2DMR-8G2/i2DMRiG2 Motherboard.

# Ultra 320 SCSI Connectors (\*i2DMR-8G2 only)

Refer to the table below for the pin definitions of the Ultra 320 SCSI connectors: SCSI A (located on J18), and SCSI B (located on J3.)

| 6                                                                                      | 8-pin Ultra 320SCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Co | onnectors (J1                                                                          | 8 and J3)                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector<br>Contact                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | Connector<br>Contact                                                                   |                                                                                                                                                                                                                                                  |

| Number                                                                                 | Signal Names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | Number                                                                                 | Signal Names                                                                                                                                                                                                                                     |